作為全球半導體技術的領導者,三星電子宣佈,其已開始用 3nm 製程來製造 GAA 環柵電晶體晶片。可知與 5nm製程相比,優化後的 3nm 製程可在收縮 16% 面積的同時,降低 45% 的功耗並提升 23% 的性能。

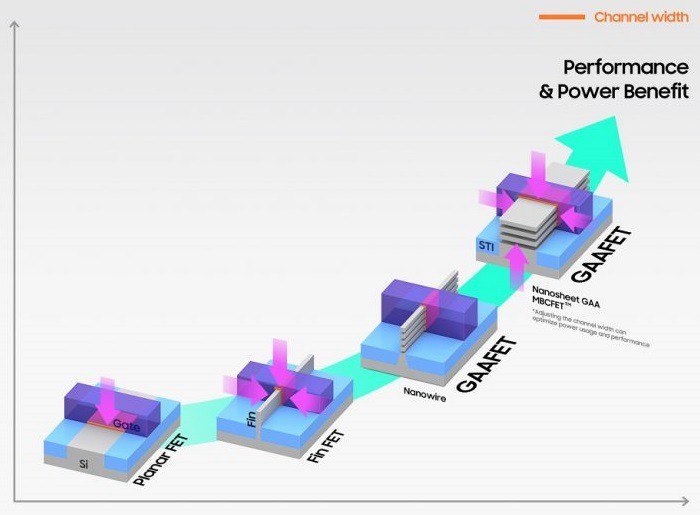

據悉,為突破鰭式場效電晶體(FinFET)的性能限制,三星選擇了多橋通道 FET(簡稱 MBCEFT)技術來製造首批 GAA 電晶體晶片。通過下調電壓水平來提升能源效率,同時增加驅動電流以提升性能。

目前三星正在努力推動 3nm GAA 電晶體和相關半導體晶片在高性能、低功耗計算領域的採用,並且計畫將相關優勢推廣到移動處理器。

▲ 左起為公司副總裁 Michael Jeong,執行副總裁 Ja-Jum Ku 和代工業務副總裁 Sang Bom Kang

▲ 左起為公司副總裁 Michael Jeong,執行副總裁 Ja-Jum Ku 和代工業務副總裁 Sang Bom Kang

三星電子總裁兼代工業務負責人 Siyoung Choi 博士表示,通過展示業內領先的下一代晶片製造工藝,三星希望在高 K 金屬柵極、FinFET 和 EUV 之外,通過 3nm MBCEFT 工藝來繼續保持競爭優勢。期間三星將保持積極創新,並建立有助於加速實現技術成熟的流程。

與使用更窄通道的奈米線 GAA 方案相比,三星專有技術選擇了更寬的通道。該公司有能力調節 3nm GAA 奈米片的通道寬度,結合優化的功耗與性能表現,以滿足客戶的各種需求。

此外 GAA 的設計靈活性,對於設計技術的協同優化(DTCP)也非常有利 —— 有助於增強功耗、性能和面積(PPA)等方面的優勢。

與 5nm 公司相比,三星電子初代 3nm GAA 技術可較 5nm 降低多達 45% 的功耗,同時提升 23% 的性能和減少 16% 的面積佔用。

展望未來,三星第二代 3nm 技術更是可以將功耗降低多達 50%,同時提升 30% 的性能和減少 35% 的面積佔用。

至於台積電,先前曾對外說明3奈米技術將延用FinFET(鰭式場效電晶體),預計3奈米製程將在下半年正式量產,在2奈米時才會進入到GAA技術製程,時程會在2025年左右。

台積電總裁魏哲家在上季法說會上表示,N3(3奈米製程)將使用FinFET電晶體架構來提供客戶最成熟的技術、最好的效能及最佳的成本,N3時程沒有改變,預計受HPC和智慧型手機應用所驅動,將在2022年下半年量產並具備良好良率。

加入T客邦Facebook粉絲團 固定链接 '三星電子宣佈開始用3奈米製程生產GAA環柵電晶體晶片' 提交: June 30, 2022, 10:49pm CST